This year, for The ConFab 2012, an entire session is devoted to Advanced Packaging and Progress in 3D Integration. The session chair, Abe Yee, is Director of Advanced Technology and Package Development, Nvidia Corp. The speakers will be:

• David McCann, Senior Director for Packaging R+D, GLOBALFOUNDRIES

• Sandeep Bharathi, Vice President of Engineering, Xilinx

• Ron Huemoeller, Senior Vice President, 3DAmkor

• Bill Chen, ASE Fellow and Sr. Technical Adviser, ASE

The focus of the session will be, in part, on 3D integration which continues to offer the promise of packing ever-higher amounts of functionality into a smaller area. We’ll also be focusing on the significant progress that continues to be made in traditional packaging (such as package-on-package and wafer level packaging).

The abstracts are still coming in, but Ron Huemoeller, for example, plans to discuss some of the challenges and opportunities for high density 3DIC Through Silicon Via (TSV) product technologies in the semiconductor industry. He says that TSV product technology offers significant opportunity in the advanced product sector of the semiconductor industry as compared to traditional System on Chip (SOC) methods for packaging die. The first part of this presentation will focus on the opportunities provided by TSV product technology in the following key areas: performance and power improvement, form factor reduction and in cost reduction at the system level. The second part of this presentation will focus on the challenges remaining in bringing this new product technology to high volume production as well as anticipated product launch dates. Particular focus will be given to the issues surrounding supply chain constraint as well as the issues associated with current state of the art approaches to completing the die stacking of these complex package structures.

A strong focus on packaging was also in evidence in 2011, with a session featuring John Waite (GLOBALFOUNDRIES), Raj Pendse (STATS ChipPAC), Robert Darveaux (Amkor), and Nick Yu (Qualcomm).

• John Waite presented “Supply Chain Reaction: A Collaborative Approach to Packaging Innovation”

• Raj Pendse presented “3D Packaging Evolution from an Outsourced Semiconductor Assembly and Test (OSAT) Perspective”

• Nice Yu presented “3D Through Si Stacking Technology,” and

• Robert Darveaux presented “Supply Chain Challenges for 3D Integration of Memory and Logic Devices using TSVs.”

A recurring theme among the presentations was that 3D integration shows tremendous promise, particularly with many fabless companies, yet many barriers remain. "We firmly believe 3D will provide a better form factor and better system level performance," said Nick Yu, VP of technology development at Qualcomm. He believes that smart phones and the demand they create for wide I/O memory stacked on logic could be the key enabler for through-silicon via (TSV) technology. "We really think it can bring the best of all worlds into your mobile handset," he said. "We think the smart phone space is really the right application for 3D TSV stacking." Growth in this market drives a lot of volume, which will drive down the cost and drive adoption, thus justifying the industry's investment.

At the time, Yu said Qualcomm is pushing for implementation by 2013, and that over the last four years they have already completed a lot of engineering work with the supply chain and demonstrated the concept. It's a little bit of a "chicken-and-egg" situation, he noted, because a driver product is needed to acquire process learning and drive the product ramp, but there are "no real show-stopper or intrinsic technical issues," he said.

Supply chain needs a 3D ecosystem, as 3D is disruptive to how we do things today. SOURCE: Nick Yu, Qualcomm.

Wide I/O memory on logic provides significantly more bandwidth. The memory industry's view is that as smart phones blur the lines between tablets and hand laptops, demand for memory bandwidth will be nearly insatiable. To enable that, standards are needed and JEDEC is going to finish the wide memory standardization by the end of 2011. Memory vendors will have parts sampling in 2012, all targeting end-product going to market by 2013, according to Yu (again, speaking in 2011).

What's not quite there yet, though, according to Yu and other presenters at The ConFab, is the 3D supply chain. "3D really ties a lot of other players together and it has this really complicated cobweb type of relationship," he said. "It is, in a sense, quite disruptive to the supply chain. That's certainly one of the major challenges for a fabless company like Qualcomm. We've been spending a lot of time and resources to work with the supply chain for the last four years on this."

Other business model questions: Who ultimately owns the dies? Who owns the inventory? And does the "pass-through" business model work? How is it going to be funded? Who owns the integration process in the end, and who owns yield? There are no easy answers and that’s part of what The ConFab is all about – giving people a forum to ask those questions and get answers.

The good news is that companies such as Qualcomm appear to be committed to making it work. "We really thought about all those challenges and we've set out to work with the industry, leveraging some of the standards bodies and really pulling together different players in the supply chain to work through that," Yu said. "There's a lot of good will and intent in the industry, but I don't think there's enough leadership."

John Waite, VP, packaging development and central engineering at GLOBALFOUNDRIES, presented noted that, since packaging costs are the dominant contributor to the value chain, designers need to select the right combination of silicon and packaging technologies to achieve performance and cost goals.

What enables success in the More Moore realm? Waite listed diverse options for wafer bumping (lead-free, copper pillar, lead and high-lead solders used in bond on pad, repassivation or redistribution [RDL] designs) and package form factor (QFP/QFN, BGA and flip chip, wafer-level chipscale packages [WLCSP]), as well as vertical options that take advantage of Z space (stacked chips, system in package [SiP]). These each have tradeoffs of cost, time, and density/performance, and customers must make packaging choices with these goals in mind.

Packaging influences the front end. SOURCE: John Waite, GLOBALFOUNDRIES.

Packaging increasingly requires attention on the frontend because of the packaging demand on the wafer. The frontend, backend, and system suppliers must collaborate in chip development. Early engagement, EDA tool flow optimization, turnkey wafer-to-package assembly, and other risk reduction strategies take a design from R&D into high-volume manufacturing.

While integrated fabless companies are ramping up leading-edge 3D IC designs, the lack of standards is holding back the 3D ecosystem. Traditional business models also don't support the boundary-breaking 3D design and process steps. Yu supports integration via standards bodies and research consortia to bring design and manufacturing standards to the 3D arena. Consider Yu's questions: Who owns the die? Who holds the inventory? How are pass-through costs funded? Who owns the integration process? Who owns the yield? Is the additional risk of TSV worth the benefits over wire-bonded stacks? Is a fabless design company or an IDM the way to go? The key question here is who acts as the "3D aggregator"? Foundry, memory company, OEM, fabless, OSAT?

Raj Pendse, VP of product and technology marketing at STATS ChipPAC and Robert Darveaux, CTO of Amkor, covered this supply chain integration from the dedicated packaging house perspective. Pendse presented "3D Packaging Evolution from an OSAT Perspective." Darveaux spoke on "Supply Chain Challenges for 3D Integration of Memory and Logic Devices using TSVs."

Material flow and infrastructure evolution. SOURCE: Dr. Raj Pendse, STATSChipPAC Inc.

Pendse sees synergies and intersections among parallel developments in the three areas of packaging technology (i.e. traditional die and package stacking on substrates, fan-in and fan-out wafer level packaging and 3D Si integration). With these new process technologies, the OSAT industry's role is transformed. Pendse channels wafer bumping, thinning, and other tasks into an in-between space for the Si foundry and OSAT to determine logical hand off points. Many of these processes can be done in both -- the question to ask is who can do it better in each scenario? Is TSV fabrication best handled in the fab, with the OSAT taking over via fill and silicon interconnect? Pendse also spoke on "bridge" technologies -- interposers, super-thin package-on-package, TSV hybridized with fan-out wafer-level packages (FOWLP) -- that play an interim role in the commercialization of 3D. Pendse shared a typical OSAT TSV roadmap through 2013 with the attendees.

Darveaux compared the relative ease of sourcing, assembly, and test of package-on-package (POP) with the challenges of TSV: difficult to test high-density area array contact pads or bumps; bare or partially assembled memory and logic die that are difficult to burn in adequately; a newer joining technology not widely available to OEMs and contract assemblers; a poorly characterized joining process yield; and, due to the immaturity of the test, burn-in, and assembly; unclear ownership of defect liability. This applies to the "2.5D" interposer strategy as well as pure 3D TSV stacks. Interconnect processes are too new and done in too small sample sizes to lead to industry agreement on the right method: die-to-die first or die-to-laminate first? Interposer in singulated format or wafer format?

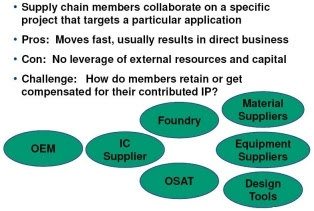

Consortium collaboration model.

Supply chain collaboration model.

SOURCE: Robert Darveaux, Amkor Technology.

These problems cannot be resolved by technologies or business models alone, he said. TSV processes can be standardized and characterized, with the resource-sharing model of consortia or the faster but potentially messy supply chain collaboration on specific projects. Both offer pros and cons, and fit different needs of the industry.

Also in 2011, Raj Jammy, VP of materials and emerging technologies at SEMATECH, covered a broad swath of CMOS scaling drivers, system and device trends, and infrastructure requirements, many of which have a direct impact on packaging. System-level trends, such as smart phones, mobile computing (e.g., iPads), and cloud computing are driving requirements for low- and ultralow-power logic with multi-core/multi-modules, dense 3D nonvolatile memory RAM for SSDs, and dense DRAMs. There is also a move to SoCs, along with high levels of functional integration and faster data transfer between modules and chips.

At the system level, the implications for devices include an even greater need for leakage reduction, and wide-band intra-chip and inter-chip interconnects. At the device level, architectural transitions to 3D FinFETs, III-V FETs, 3D flash memories, RRAM, STTRAM, SoCs, and 3D TSVs, and even photonic interconnects are being evaluated. Each of these alternatives poses specific challenges -- but common to all are strong infrastructural needs to be successful. Among the transitions' challenges will be new materials and/or using non-silicon materials, new models/test methods/designs, integration challenges, as well as processes, materials, tools, and packaging.

The biggest challenges for high-volume manufacturing of through silicon vias (TSV), Jammy said, are all through the process flow. Bonding and de-bonding is one major example, with poor throughput. Materials stresses, especially on thinned dies, are another.

SoC technologies are on the verge of some significant changes, Jammy predicts. For example, an entire smartphone could be fit onto one SoC. With system in package (SiP), additional functionality will be integrated, even MEMS devices.

Packaging has a rich history in previous ConFabs going back even further. In 2010, for example, Matt Nowak, director of engineering in Qualcomm's VLSI technology group, said high-density through-silicon stacking (TSS) shows promise for very high-volume applications, but work still needs to be done to "tame" key issues in manufacturing, improve costs, and smooth out the supply-chain. He also urged standards for supply-chain handoff points, with specs and test methods to reliably manufacture TSS from multiple sources and processes, validated by experimental results (reliability, cost, yield, etc.). Target areas for initial standards include:

• Nomenclature/definitions

• TSV size, tier thickness, via fill material

• Tier-to-tier pin locations and assignments

• Key physical design rules

• Microbump and passivation materials properties and geometries

• Reliability test methods

• Metrology

• Thin wafer shipping

Also in 2010, Jim Clifford, SVP/GM of operations at Qualcomm CDMA Technologies, talked at length about the convergence of wireless connectivity and increasing performance requirements, the resulting technical (and economic) challenges brought upon supporting technologies, and the importance of "early engagement" to cost-effectively research and develop products. He, too, stuck to a common theme across many ConFabs over the years: Collaboration across the entire eco-system. Speaking to Qualcomm's bread-and-butter, Clifford highlighted the "integrated fabless model" in which fabless companies engage with foundries very early on. In the IFM model, development starts toward the end of module development; then investing in IP/design/product development (including integration/qualification), and then production. An aligned ecosystem across the entire value chain (foundry, customers, research, EDA, IP, packaging, and testing) is required to optimize product innovation and execution. Clifford highlighted the need for early engagement with research organizations for a "co-design start," a phase dubbed "early pathfinding," which starts before and extends beyond module development and into integration/product development.

Prior to that, system-level considerations of 3D ICs were presented by Tom Gregorich, VP of Qualcomm, in a session discussing the "Economic implications of 3D" at the ConFab in Las Vegas in 2008. He reminded the audience that end-users of portable electronics products -- such as cellphones and PDA -- expect reliable functionality regardless of dropping, kicking, or washing the device. Delivering ever greater functionality in essentially the same robust package is a mandate for innovative concepts such as 3D.

Subramanian Iyer, distinguished engineer and chief technologist of IBM's Systems and Technology Group, explained the economic considerations behind 3D microprocessors. He noted that the economics of any new technology need to be assessed with respect to the advantages of other competing approaches that provide the same or similar benefits. Both embedded DRAM in a system-on-chip (SoC) and stand-alone DRAM as part of a system-in-package (SiP) have been well established as 2D solutions, so any 3D approach must be compared to these proven techniques. Iyer made his case by examining the relatively straightforward but very important challenge of balancing memory with 64 processor cores in a system.

Beyond today's stacked chips in a package may come higher performance 3D stacked ICs using through-silicon vias (TSV) to interconnect layers, according to Sitaram Arkalgud, who spoke on the economic implications of 3D.

In short, during the 8 years of The ConFab’s history, packaging topics have always been at the forefront, and will continue to be this year and in the future.

No comments:

Post a Comment